Document No : UniKL MFI\_SD\_AC41 Revision No: 02 Effective Date: 01 December 2008

SET A

# UNIVERSITI KUALA LUMPUR Malaysia France Institute

# FINAL EXAMINATION SEPTEMBER 2013 SESSION

SUBJECT CODE : FSD23102

SUBJECT TITLE : MICROPROCESSOR

LEVEL : DIPLOMA

TIME / DURATION :

(2 HOURS)

DATE :

#### **INSTRUCTIONS TO CANDIDATES**

- 1. Please read the instructions given in the question paper CAREFULLY.

- 2. This question paper is printed on both sides of the paper.

- 3. Please write your answers on the answer booklet provided.

- 4. Answer should be written in blue or black ink except for sketching, graphic and illustration.

- 5. This question paper consists of TWO (2) sections. Section A and B. Answer all questions in Section A. For Section B, answer two (2) questions only.

- Answer all questions in English.

THERE ARE 9 PAGES OF QUESTIONS AND 2 PAGES OF APPENDICES, EXCLUDING THIS PAGE.

**SECTION A (Total: 60 marks)**

INSTRUCTION: Answer ALL questions.

Please use the answer booklet provided.

#### **Question 1**

(a) Provide the definition of microprocessor.

(2 marks)

(b) State TWO (2) system buses in M68K microprocessor.

(2 marks)

(c) Describe the principles of CPU Execution Cycle for M68K Microprocessor.

(3 marks)

(d) CPU is the "master" component in Microprocessor System. List THREE (3) main components of CPU.

(3 marks)

(e) Define Reprogrammable System and Embedded System and give TWO (2) examples for each application.

(6 marks)

(f) Differentiate between RAM and ROM in terms of data storage and computer application process performed by both memory types.

(4 marks)

1

#### **Question 2**

- (a) Fill in the blanks with correct answers.

- i. The function of Condition Code Register is \_\_\_\_\_\_. This register consist of \_\_\_\_\_\_ bits flags which are \_\_\_\_\_.

(3 marks)

ii. 1 long word = \_\_\_\_\_ bits.

(3 marks)

iii. If the interrupt signal level has the highest priority the status for Interrupt Mask Bits (IMB) is \_\_\_\_\_.

(1 mark)

- (b) Describe the function of Program Counter and state the size in bits of this register.

(3 marks)

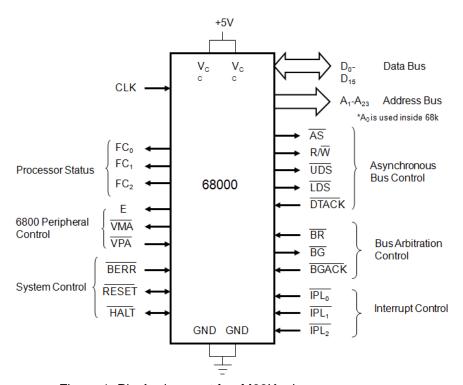

- (c) Figure 1 shows the Pin Assignment for M68K microprocessor. Based on the figure answer the following questions:

Figure 1: Pin Assignment for M68K microprocessor.

i. List THREE (3) states of RW pin in Asynchronous Bus Control.

(3 marks)

ii. Describe the function of System Control pins.

(3 marks)

(d) Figure 2 shows the example of Interrupt Process. The External Peripheral has important task while M68K is executing its instructions normally. The interrupt signal has been request by External Peripheral Interrupt Control Pin. If the external interrupt higher than current process, briefly explain what are the next steps performed by M68K.

Figure 2: Interrupt Process

(4 marks)

#### **Question 3**

Convert and perform the arithmetic operation below and show the conversion procedure algorithmically.

(a) Convert **453** to hexadecimal form.

(3 marks)

(b) Convert **\$F4A** to binary form.

(2 marks)

(c) Convert %10011.111 to decimal form.

(2 marks)

(d) Convert signed number **\$FC** to decimal form.

(3 marks)

(e) By using *two*'s *complement* binary arithmetic, compute the following operation.

**Note:** Your calculations should be in 8-bit format for integer numbers.

70 - \$1F

(5 marks)

(f) Based on your answers in Question 3(d), state the status of C-bit and Z-bit in Condition Code Register.

(2 marks)

(g) Describe the function of V-bit in Condition Code Register and state the status based on your answers in Question 3 (d).

(3 marks)

**SECTION B (Total: 40 marks)**

INSTRUCTION: Answer TWO (2) questions only

Please use the answer booklet provided.

#### **Question 4**

(a) Figure 3 shows the initial values of Address Registers, Data Registers and memory locations in M68K microprocessor.

| Initial Values for Address<br>& Data Registers | Initial Memory |      |

|------------------------------------------------|----------------|------|

| A1 = \$600601                                  | \$600600       | \$58 |

| A2 = \$600605                                  | \$600601       | \$63 |

| A3 = \$60060A                                  | \$600602       | \$24 |

|                                                | \$600603       | \$12 |

| D0 = \$22224444                                | \$600604       | \$00 |

| D1 = \$FEDCBA12                                | \$600605       | \$FF |

| D2 = \$55556666                                | \$600606       | \$02 |

| D3 = \$0000007                                 | \$600607       | \$BB |

|                                                | \$600608       | \$00 |

|                                                | \$600609       | \$00 |

|                                                | \$60060A       | \$05 |

Figure 3: Initial values for Address Registers, Data Registers and memory.

Explain the contents of the affected registers or memory locations when each of the following instructions are executed. Each instruction is executed independently. The initial values of the registers and memory are the same before each instruction is executed.

| i.   | ADD.B   | (A3), D3     |           |

|------|---------|--------------|-----------|

|      |         |              | (2 marks) |

| ii.  | MOVE.B  | \$06(A1), D0 |           |

|      |         |              | (2 marks) |

| iii. | MOVE. L | D2, \$600600 |           |

|      |         |              | (2 marks) |

| iv.  | MOVE. B | \$600605, D1 |           |

|      |         |              | (2 marks) |

(b) Find the destination target and source for instruction code below.

## MOVE.W D1, D0

(2 marks)

(c) Write complete assembly language programs to divide unsigned numbers \$4D with \$04. Your programs also should store \$4D and \$04 in two data registers and start with memory location \$1000.

(5 marks)

(d) Based on the Question 4(c), compute the answers from that division operation and illustrate it in terms of data arrangement. State the status for V-bit flag based on the final answer.

(5 marks)

#### **Question 5**

(a) Table 1 shows four (4) unsigned 8-bits data that need to be stored into allocated memory address. Then, these four (4) data will be added and the result will be stored in D0. Consider the assembly language programs below and continue the programs with your answers by using do-while loop. Your programs should be complete with comments.

Table 1: Data stored in equivalent memory address

| Data Value | Memory Address |

|------------|----------------|

| #\$2A      | \$3000         |

| #\$41      | \$3001         |

| #\$43      | \$3002         |

| #\$30      | \$3003         |

| START | ORG    | \$400400                                   |   |

|-------|--------|--------------------------------------------|---|

|       | MOVE.B | #\$2A,\$3000 ; Put \$2A into address \$300 | 0 |

|       | MOVE.B | #\$41,\$3001 ; Put \$41 into address \$300 | 1 |

|       | MOVE.B | #\$43,\$3002 ; Put \$43 into address \$300 | 2 |

|       | MOVF.B | #\$30.\$3003 : Put \$30 into address \$300 | 2 |

(15 marks)

(b) Consider the assembly language instruction below and discuss on the Addressing Mode for this instruction.

MOVE.B #\$2A,\$3000

(5 marks)

#### **Question 6**

(a) A post service company needs a system to calculate the volume of rectangular box for international shipping services. As a software engineer, you need to create an assembly language programs that will calculate the volume of rectangular box for this post service company based on the following information:

i. Memory locations \$400000 until \$400002 contain the width, height and length of rectangular, respectively as in Table 2.

|  | Table 2: Data | a stored in | equivalent | Memory | / Address |

|--|---------------|-------------|------------|--------|-----------|

|--|---------------|-------------|------------|--------|-----------|

| Memory Address | Data Value |

|----------------|------------|

| \$40000        | #\$03      |

| \$400001       | #\$02      |

| \$400002       | #\$05      |

- ii. Your programs should consist of *Address Register Indirect AddressingMode*.

- iii. Use this formula given for calculating the volume of rectangle:Volume of rectangle = width x height x length

- iv. The result must be stored at memory address \$700002.

Consider the assembly language programs below and please continue the programs with your answers based on the above informations. Your programs should be complete with comments.

| START | ORG | \$1000; programs origin start at memory \$1000      |

|-------|-----|-----------------------------------------------------|

|       | LEA | \$400000,A0; Load affected address \$400000 into A0 |

|       | LEA | \$400001,A1; Load affected address \$400001 into A1 |

|       | LEA | \$400002.A2: Load affected address \$400002 into A2 |

(15 marks)

(b) Based on Question 6 (a) compute the result stored in memory address \$700002. Prove your answer with calculation.

(3 marks)

(c) Briefly explain on the MOVEA instruction code.

(2 marks)

## **END OF QUESTIONS**

**APPENDIX 1: M68K Datasheet**

| Opcode            | Ci-re           | Operand                | CCR     |         | H-             | time   | Addus | r c             | nunce  | d-dostina              | tion o | -nith- | n judio     | placemen  | +              | Operation                                            | Description                                                                     |

|-------------------|-----------------|------------------------|---------|---------|----------------|--------|-------|-----------------|--------|------------------------|--------|--------|-------------|-----------|----------------|------------------------------------------------------|---------------------------------------------------------------------------------|

| ohcode            | BWL             | s.d                    | XNZVC   |         |                | (An)   |       | S S=SI<br>-(An) |        | o=oestina<br>(i.An.Rn) |        |        |             |           |                | uperation                                            | vescription                                                                     |

| ABCD              | B B             | Dv.Dx                  | *[]*[]* | un<br>e | An -           | (An)   | (An)+ | -(An)           | (I,An) | (I,An,Kn)              | aus.w  | aus.L  | (I,PL)<br>- | (I,FL,KN) | #11            | $Dy_{in} + Dx_{in} + X \rightarrow Dx_{in}$          | Add BCD source and eXtend bit to                                                |

| AUGU              | U               | -(Ay),-(Ax)            | -0-0-   | E       | -              |        | -     |                 |        | -                      |        | -      |             | -         | -              | $-(Ay)_{10} + -(Ax)_{10} + X \rightarrow -(Ax)_{10}$ | destination, BCD result                                                         |

| ADD 4             | BWL             | s,Dn                   | ****    | е       | S              | S      | s     | 8               | S      | S                      | S      | S      | S           | S         | -4             | $s + Dn \rightarrow Dn$                              | Add binary (ADDI or ADDQ is used when                                           |

| AUU               | DML             | Dn.d                   |         |         | d <sup>4</sup> | d<br>S | d d   | q               | d<br>S | d<br>S                 | d      | d      | 2           | S         | 2              | S+un → un<br>Dn+d → d                                | source is #n. Prevent ADDQ with #n.L)                                           |

| ADDA 4            | WL              | _                      |         | 9       | _              | _      |       |                 |        |                        |        |        |             | -         | _              |                                                      |                                                                                 |

|                   |                 | s,An                   | ****    | S       | 9              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | S              |                                                      | Add address (.W sign-extended to .L)                                            |

| ADDI 4            | BWL             | #n,d                   | ****    | d       | -              | d      | d     | d               | d      | ď                      | d      | d      | -           | -         | -              | #n + d → d                                           | Add immediate to destination                                                    |

| ADDQ 4            | BWL             | #n,d                   | ****    | d       | d              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | S              |                                                      | Add quick immediate (#n range: 1 to 8)                                          |

| ADDX              | BWL             | - /1                   | ****    | е       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | $Dy + Dx + X \rightarrow Dx$                         | Add source and eXtend bit to destination                                        |

| L.,               |                 | -(Ay),-(Ax)            |         | -       | -              | -      | -     | 9               | -      | -                      | -      | -      | -           | -         | -              | $-(Ay) + -(Ax) + X \rightarrow -(Ax)$                |                                                                                 |

| AND 4             | BWL             | s,Dn                   | -**00   | е       | -              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | s*             | s AND Dn $\rightarrow$ Dn                            | Logical AND source to destination                                               |

|                   |                 | Dn,d                   |         | е       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | -              | On AND d → d                                         | (ANDI is used when source is #n)                                                |

| ANDI 4            | BWL             | #n,d                   | -**00   | d       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | S              |                                                      | Logical AND immediate to destination                                            |

| ANDI 4            | В               | #n,CCR                 | =====   | -       | -              | -      |       | -               | -      | -                      | ,      | ,      |             | -         | S              | #n AND CCR → CCR                                     | Logical AND immediate to CCR                                                    |

| ANDI 4            | W               | #n,SR                  |         | -       | -              | -      | -     | -               | -      | -                      | -      |        | -           | -         | S              | #n AND SR → SR                                       | Logical AND immediate to SR (Privileged)                                        |

| ASL               | BWL             | Dx,Dy                  | ****    | е       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | X T                                                  | Arithmetic shift Dy by Dx bits left/right                                       |

| ASR               |                 | #n,Dy                  |         | d       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | s              |                                                      | Arithmetic shift Dy #n bits L/R (#n: 1 to 8)                                    |

|                   | W               | d                      |         | -       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | -              | □ C X                                                | Arithmetic shift ds 1 bit left/right (.W only)                                  |

| Bee               | BW <sup>3</sup> | address <sup>2</sup>   |         | -       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | if cc true then                                      | Branch conditionally (cc table on back)                                         |

| 200               |                 |                        |         |         |                |        |       |                 |        |                        |        |        |             |           |                | address → PC                                         | (8 or 16-bit ± offset to address)                                               |

| BCHG              | B L             | Dn.d                   | *       | e¹      | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | -              | NOT(bit number of d) $\rightarrow$ Z                 | Set Z with state of specified bit in d then                                     |

| 100110            |                 | #n,d                   |         | ď       | _              | d      | d     | ď               | ď      | ď                      | ď      | d      | _           | _         | s              | NOT(bit n of d) $\rightarrow$ bit n of d             | invert the bit in d                                                             |

| BCLR              | BL              | Dn.d                   | *       | e       | -              | d      | d     | d               | d      | ď                      | ď      | d      | -           | -         | -              | NOT(bit number of d) $\rightarrow$ Z                 | Set Z with state of specified bit in d then                                     |

| DUCLIN            | U L             | #n.d                   |         | ď       |                | d      | d     | d               | d      | ď                      | ď      | d      |             | _         | S              | 0 → bit number of d                                  | clear the bit in d                                                              |

| BRA               | BW <sup>3</sup> | address <sup>2</sup>   |         | u<br>-  | -              | - u    | - U   | - u             | - u    | - u                    | - U    | - u    | -           | -         | 2              | address → PC                                         | Branch always (8 or 16-bit ± offset to addr)                                    |

|                   |                 |                        | *       |         | -              | _      | d     |                 |        |                        |        |        | -           | -         | -              |                                                      |                                                                                 |

| BSET              | ΒL              | Dn.d                   |         | e       | -              | d      | _     | d               | d -    | d                      | d      | d      |             |           | ı              | NOT( bit n of d ) $\rightarrow$ Z                    | Set Z with state of specified bit in d then                                     |

| non               | mw3             | #n,d                   |         | ď       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | _              | 1 → bit n of d                                       | set the bit in d                                                                |

| BSR               | BW3             | address <sup>2</sup>   |         | -       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | $PC \rightarrow -(SP)$ ; address $\rightarrow PC$    | Branch to subroutine (8 or 16-bit ± offset)                                     |

| BTST              | ΒL              | Dn,d                   | *       | e.      | -              | d      | d     | d               | d      | d                      | d      | d      | d           | d         | -              | NOT( bit $Dn 	ext{ of } d$ ) $\rightarrow Z$         | Set Z with state of specified bit in d                                          |

|                   |                 | #n,d                   |         | ď       | -              | d      | d     | d               | d      | d                      | d      | d      | d           | d         | S              | NOT(bit #n of d ) $\rightarrow$ Z                    | Leave the bit in d unchanged                                                    |

| CHK               | W               | s,Dn                   | -*000   | 9       | -              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | S              |                                                      | Compare Dn with O and upper bound [s]                                           |

| CLR               | BWL             | d                      | -0100   | d       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | -              | 0 → d                                                | Clear destination to zero                                                       |

| CMP 4             | BWL             | s,Dn                   | -****   | е       | s <sup>4</sup> | S      | S     | S               | S      | S                      | S      | S      | S           | S         | s4             | set CCR with Dn - s                                  | Compare Dn to source                                                            |

| CMPA <sup>4</sup> | WL              | s,An                   | _****   | S       | е              | S      | S     | S               | S      | S                      | 2      | 2      | S           | S         | S              | set CCR with An - s                                  | Compare An to source                                                            |

| CMPI 4            | BWL             | #n,d                   | -****   | d       | -              | d      | d     | d               | d      | d                      | d      | d      | -           | -         | S              | set CCR with d - #n                                  | Compare destination to #n                                                       |

| CMPM 4            | BWL             | (Ay)+,(Ax)+            | -****   | -       | -              | -      | е     | -               | -      | -                      | -      | -      | -           | -         | -              | set CCR with (Ax) - (Ay)                             | Compare (Ax) to (Ay); Increment Ax and Ay                                       |

| DBcc              | W               | Dn,addres <sup>2</sup> |         | -       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | if cc false then { Dn-1 → Dn                         | Test condition, decrement and branch                                            |

|                   |                 |                        |         |         |                |        |       |                 |        |                        |        |        |             |           |                | if On ⇔ -1 then addr →PC }                           | (16-bit ± offset to address)                                                    |

| DIVS              | W               | s,Dn                   | -***0   | е       | -              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | S              | ±32bit Dn / ±16bit s → ±Dn                           | Dn= [ 16-bit remainder, 16-bit quotient ]                                       |

| DIVU              | W               | s,Dn                   | -***0   | е       | -              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | s              | 32bit Dn / 16bit s → Dn                              | Dn= [ 16-bit remainder, 16-bit quotient ]                                       |

| EOR 4             | RWI             | Dn.d                   | -**00   | е       | -              | d      | d     | d               | d      | d                      | ų.     | d      | -           | -         |                | On XOR d → d                                         | Logical exclusive OR Dn to destination                                          |

| FORI 4            | BWL             | #n.d                   | -**00   | d       | _              | d      | d     | d               | d      | ď                      | d      | d      | _           | -         | S              | #n XDR d → d                                         | Logical exclusive OR #n to destination                                          |

| EORI 4            | R               | #n,CCR                 |         | u       | ŀ              | -      | - u   | - u             | - u    | - u                    | -      | -      | -           | -         | -              | #n XDR CCR → CCR                                     | Logical exclusive DR #n to CCR                                                  |

|                   | _               | -                      |         | -       | <u> </u>       | -      | -     |                 |        |                        |        | _      |             |           | S              |                                                      | Logical exclusive OR #n to SR (Privileged)                                      |

| EORI 4            | W               | #n,SR                  | =====   | -       | -              | _      |       | -               | -      | -                      | -      |        | -           | -         | S              |                                                      |                                                                                 |

| EXG               | L               | Rx,Ry                  | -**00   | 9       | 9              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | register ← → register                                | Exchange registers (32-bit only)                                                |

| EXT               | WL              | Dn                     | -**00   | d       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              |                                                      | Sign extend (change .B to .W or .W to .L)                                       |

| ILLEGAL           |                 |                        |         | -       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | $PC \rightarrow -(SSP); SR \rightarrow -(SSP)$       | Generate Illegal Instruction exception                                          |

| JMP               |                 | d                      |         | -       | -              | d      | -     | -               | d      | d                      | d      | d      | d           | d         | -              | ↑d → PC                                              | Jump to effective address of destination                                        |

| JSR               |                 | d                      |         | -       | -              | d      | -     | -               | d      | d                      | d      | d      | d           | d         | -              | $PC \rightarrow -(SP); \uparrow d \rightarrow PC$    | push PC, jump to subroutine at address d                                        |

| LEA               | L               | s,An                   |         | -       | е              | S      | -     | -               | S      | S                      | S      | S      | S           | S         | -              | ↑s → An                                              | Load effective address of s to An                                               |

| LINK              |                 | An,#n                  |         | -       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | $An \rightarrow -(SP); SP \rightarrow An;$           | Create local workspace on stack                                                 |

|                   |                 |                        |         |         |                |        |       |                 |        |                        |        |        |             |           |                | $SP + \#n \rightarrow SP$                            | (negative n to allocate space)                                                  |

| LSL               | BWL             | Dx,Dy                  | ***0*   | е       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | X                                                    | Logical shift Dy, Dx bits left/right                                            |

| LSR               |                 | #n,Dy                  |         | d       | -              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | s              | C - C - X                                            | Logical shift Dy, #n bits L/R (#n: 1 to 8)                                      |

| '                 | W               | d                      |         | -       | -              | d      | d     | d               | d      | d                      | d      | d      | _           | -         | -              | 0 → C                                                | Logical shift d 1 bit left/right (.W only)                                      |

| MOVE 4            | BWL             | s,d                    | -**00   | е       | s <sup>4</sup> | 6      | е     | 6               | 8      | 8                      | В      | 9      | S           | S         | s <sup>4</sup> | s → d                                                | Move data from source to destination                                            |

| MOVE              | W               | s,CCR                  | =====   | S       | -              | S      | S     | S               | S      | S                      | S      | S      | S           | S         | S              | s → CCR                                              | Move source to Condition Code Register                                          |

| MOVE              | w               | s,SR                   |         | S       | -              | S      | S     |                 |        |                        | S      | S      | S           |           | S              | s → SR                                               | Move source to Status Register (Privileged)                                     |

| MOVE              | W               | SR,d                   |         | d       | -              | q      | d d   | s<br>d          | s<br>d | s<br>d                 | q      | q      | - 2         | S<br>-    | 2              | $SR \rightarrow d$                                   | Move Status Register to destination                                             |

|                   | "               |                        |         | a       | _              | 0      | 0     | Ü               | ú      | Ü                      | Ü      | Ü      | -           | -         | -              |                                                      | Move Status Register to destination  Move User Stack Pointer to An (Privileged) |

| MOVE              | L               | USP,An                 |         | -       | d              | -      | -     | -               | -      | -                      | -      | -      | -           | -         | -              | USP → An                                             |                                                                                 |

|                   | DIVI            | An,USP                 | Waterse | -       | S              |        |       |                 |        |                        |        | -      |             | # DC D :  | -              | An → USP                                             | Move An to User Stack Pointer (Privileged)                                      |

|                   | B₩L             | s,d                    | XNZVC   | Dn      | An             | (An)   | (An)+ | -(An)           | (i,An) | (i,An,Rn)              | abs.W  | abs.L  | (i,PC)      | (i,PC,Rn) | #n             |                                                      |                                                                                 |

# **APPENDIX 1: M68K Datasheet (continue)**

| Oncode                                | Size       | Operand     | CCR   |        | ffer | rtive  | Addres  | 2=2 2 | nurre  | d=destina | tion e    | =eithe | r i=dis | placemen  | ıt             | Operation                                        | Description                                                         |

|---------------------------------------|------------|-------------|-------|--------|------|--------|---------|-------|--------|-----------|-----------|--------|---------|-----------|----------------|--------------------------------------------------|---------------------------------------------------------------------|

| -poone                                | BWL        | s.d         | XNZVC | Dn     | An   | (An)   | (An)+   | -(An) | (i,An) | (i.An.Rn) | abs.W     | abs.L  | (i.PC)  | (i.PC.Rn) | #n             | Spor acion                                       | Door pron                                                           |

| MOVEA4                                | WL         | s.An        |       | S      | е    | S      | S       | S     | S      | S         | S         | S      | S       | S         | S              | s → An                                           | Move source to An (MOVE s.An use MOVEA)                             |

| MUNEW4                                | WI         | Rn-Rn.d     |       | -      | -    | d      | -       | q     | 4      | ď         | d         | 4      | -       | -         | -              | Registers → d                                    | Move specified registers to/from memory                             |

| I I I I I I I I I I I I I I I I I I I | ""         | s.Rn-Rn     |       | _      | _    | s      | s       |       | S      | S         | s         | S      | S       | s         |                | s → Registers                                    | (.W source is sign-extended to .L for Rn)                           |

| MOVEP                                 | WL         | Dn.(i.An)   |       | S      | -    | -      | -       | -     | q      | -         | -         | -      | -       | -         | -              | Dn → (i,An)(i+2,An)(i+4,A.                       | Move Dn to/from alternate memory bytes                              |

| Hotel                                 | ""         | (i.An).Dn   |       | d      | _    | _      | _       | _     | S      | _         | _         | _      | _       | _         | _              | $(i,An) \rightarrow Dn(i+2,An)(i+4,A.$           | (Access only even or odd addresses)                                 |

| MOVEQ <sup>4</sup>                    | Т          | #n Dn       | -**00 | Ч      | -    | -      | -       | -     | -      | -         | -         | _      | -       | -         | 2              | #n → Dn                                          | Move sign extended 8-bit #n to Dn                                   |

| MULS                                  | W          | s.Dn        | -**00 | e      | -    | S      | s       | S     | S      | S         | S         | S      | S       | S         |                | ±16bit s * ±16bit Dn → ±Dn                       | Multiply signed 16-bit; result; signed 32-bit                       |

| MULU                                  | w          | s.Dn        | -**00 | e      | -    | S      | S       | S     | S      | 2         | S         | S      | S       | S         | _              | 16bit s * 16bit Dn → Dn                          | Multiply unsig'd 16-bit; result: unsig'd 32-bit                     |

| NBCD                                  | В.         | d           | *U*U* | d      |      | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              | 0 - dn - X → d                                   | Negate BCD with eXtend, BCD result                                  |

| NEG                                   | BWL        | -           | ****  | d      | -    | d      | ď       | ď     | d      | d         | d         | 4      | -       | -         | -              | 0-d → q                                          | Negate destination (2's complement)                                 |

| NEGX                                  | RWI        | -           | ****  | d      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              | 0-d-X → q                                        | Negate destination (2's complement)  Negate destination with eXtend |

| NOP                                   | DMT        | U           |       | u      | -    | - U    | - U     | - u   | - u    | - U       | - U       | - u    | -       | -         | -              | None                                             | No operation occurs                                                 |

| NOT                                   | DWI        | J           | -**00 | -      | -    | d      | d       |       | d      |           | d         |        | -       | -         | -              | NOT( d ) → d                                     |                                                                     |

| NU I                                  | BWL<br>BWL | d           | -**00 | d      | -    | _      | _       | d     |        | d         |           | d      |         |           |                |                                                  | Logical NOT destination (I's complement)                            |

| UK .                                  | DMT        | -,          | 00    | 9      | -    | S      | S       | S     | S      | S         | S         | S      | S       | S         | s <sup>4</sup> | s OR On → On                                     | Logical OR                                                          |

| nnı á                                 | DWI        | Dn,d        | -**00 | 9      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | _              | On OR d → d                                      | (ORI is used when source is #n)                                     |

| ORI 4                                 | BWL        | #n,d        |       | d      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | S              | #n OR d → d                                      | Logical OR #n to destination                                        |

| ORI 4                                 | В          | #n,CCR      | ===== | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | _              | #n OR CCR → CCR                                  | Logical OR #n to CCR                                                |

| ORI 4                                 | W          | #n,SR       | ===== | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | _              | #n OR SR → SR                                    | Logical OR #n to SR (Privileged)                                    |

| PEA                                   | L          | S           |       | -      | -    | S      | -       | -     | S      | S         | S         | S      | S       | S         | -              | ↑s → -(SP)                                       | Push effective address of s onto stack                              |

| RESET                                 |            |             |       | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | Assert RESET Line                                | Issue a hardware RESET (Privileged)                                 |

| ROL                                   | BWL        |             | -**0* | е      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | C                                                | Rotate Dy, Dx bits left/right (without X)                           |

| ROR                                   |            | #n,Dy       |       | d      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | S              |                                                  | Rotate Dy, #n bits left/right (#n: 1 to 8)                          |

|                                       | W          | d           |       | -      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              |                                                  | Rotate d 1-bit left/right (.W only)                                 |

| ROXL                                  | BWL        | Dx,Dy       | ***0* | е      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | c X                                              | Rotate Dy, Dx bits L/R, X used then updated                         |

| ROXR                                  |            | #n,Dy       |       | d      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | S              | X C                                              | Rotate Dy, #n bits left/right (#n: 1 to 8)                          |

|                                       | W          | d           |       | -      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              |                                                  | Rotate destination 1-bit left/right (.W only)                       |

| RTE                                   |            |             | ===== | -      | -    | -      | -       | -     | •      | -         | -         | •      | •       | -         | -              | $(SP)+ \rightarrow SR; (SP)+ \rightarrow PC$     | Return from exception (Privileged)                                  |

| RTR                                   |            |             | ===== | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | $(SP)+ \rightarrow CCR, (SP)+ \rightarrow PC$    | Return from subroutine and restore CCR                              |

| RTS                                   |            |             |       | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | (SP)+ → PC                                       | Return from subroutine                                              |

| SBCD                                  | В          | Dy,Dx       | *U*U* | е      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | $Dx_{10} - Dy_{10} - X \rightarrow Dx_{10}$      | Subtract BCD source and eXtend bit from                             |

|                                       |            | -(Ay),-(Ax) |       | -      | -    | -      | -       | е     | •      | -         | -         | -      | -       | -         | -              | $-(Ax)_{10}(Ay)_{10} - X \rightarrow -(Ax)_{10}$ | destination, BCD result                                             |

| Sec                                   | В          | d           |       | d      | -    | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              | If cc is true then I's $\rightarrow$ d           | If cc true then d.B = 111111111                                     |

|                                       |            |             |       |        |      |        |         |       |        |           |           |        |         |           |                | else D's $\rightarrow$ d                         | else d.B = 00000000                                                 |

| STOP                                  |            | #n          | ===== | -      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | s              | #n → SR: STOP                                    | Move #n to SR, stop processor (Privileged)                          |

| SUB <sup>4</sup>                      | BWL        | s,Dn        | ****  | е      | s    | S      | S       | S     | S      | S         | S         | S      | S       | S         | s <sup>4</sup> | Dn - s → Dn                                      | Subtract binary (SUBI or SUBQ used when                             |

|                                       |            | Dn,d        |       | е      | ď    | d      | d       | d     | d      | d         | d         | d      | -       | -         | -              | d - Dn → d                                       | source is #n. Prevent SUBQ with #n.L)                               |

| SUBA 4                                | WL         | s.An        |       | s      | е    | S      | s       | S     | S      | S         | S         | S      | S       | S         | s              | An - s → An                                      | Subtract address (.W sign-extended to .L)                           |

| SUBL 4                                | RWI        | #n d        | ****  | d      | -    | d      | d       | d     | d      | d         | ď         | d      | -       | -         |                | d - #n → d                                       | Subtract immediate from destination                                 |

| SUBQ 4                                | BWL        | #n,d        | ****  | d      | d    | d      | d       | d     | d      | d         | d         | d      | -       | -         |                | d - #n → d                                       | Subtract quick immediate (#n range: 1 to 8)                         |

| SUBX                                  | BWL        | Dv.Dx       | ****  | е      | -    | -      | -       | -     | -      | -         | -         | -      | -       | -         | -              | $Dx - Dv - X \rightarrow Dx$                     | Subtract source and extend bit from                                 |

| CODA                                  | 5          | -(Ay),-(Ax) |       | -      | _    | _      | _       | е     | _      | _         | _         | _      | _       | _         | _              | $-(Ax)(Ay) - X \rightarrow -(Ax)$                | destination                                                         |

| SWAP                                  | W          | Dn .        | -**00 | d      | _    | -      | -       | -     | -      | -         | _         | _      | _       | -         | -              | bits[31:16] ← → bits[15:0]                       | Exchange the 16-bit halves of Dn                                    |

| TAS                                   | В.         | d           | -**00 | d      | -    | d      | d       | d     | d      | d         | d         | d      | _       | -         | -              | test d→CCR: 1 →bit7 of d                         | N and Z set to reflect d, bit7 of d set to 1                        |

| TRAP                                  | u          | #n          |       | -      |      | -      | u       | - u   | - u    | - u       | - u       | - u    | -       | -         |                | $PC \rightarrow -(SSP):SR \rightarrow -(SSP):$   | Push PC and SR, PC set by vector table #n                           |

| INAF                                  |            | πil         |       |        | -    | -      |         |       |        |           | _         | _      |         |           | 2              | $(\text{vector table entry}) \rightarrow PC$     | (#n range: 0 to 15)                                                 |

| TRAPV                                 |            |             |       |        | -    | -      | -       | _     | _      | -         | _         | _      | _       | -         | -              | (vector table entry) → PL<br>If V then TRAP #7   | (#n range: u to i5)  If overflow, execute an Overflow TRAP          |

| TST                                   | BWL        | d           | -**00 | -<br>d | -    | d      | - d     | - d   | d      | - d       | d         | d      | -       | -         | -              | test d → CCR                                     | N and Z set to reflect destination                                  |

|                                       | DML        | -           |       | 0      |      | _      | _       | _     |        | 0         |           |        |         | -         | -              |                                                  |                                                                     |

| UNLK                                  | DIMI       | An          | VMPTE | -<br>D | d    | - //-> | - //->- | - (1) | - CA-V |           | -<br>-L-W | - In I | - (100) |           | -              | $An \rightarrow SP$ ; (SP)+ $\rightarrow An$     | Remove local workspace from stack                                   |

|                                       | BWL        | s,d         | XNZVC | Dn     | An   | (An)   | (An)+   | -(An) | (i,An) | (i,An,Rn) | abs.W     | abs.L  | (i,PC)  | (i,PC,Rn) | #n             |                                                  |                                                                     |

| Condition Tests (+ DR, ! NOT, ⊕ XDR; " Unsigned, " Alternate cc ) |                |           |    |                  |                       |  |  |  |  |  |  |  |

|-------------------------------------------------------------------|----------------|-----------|----|------------------|-----------------------|--|--|--|--|--|--|--|

| CC                                                                | Condition      | Test      | CC | Test             |                       |  |  |  |  |  |  |  |

| T                                                                 | true           | 1         | VC | overflow clear   | !V                    |  |  |  |  |  |  |  |

| F                                                                 | false          | 0         | ΛZ | overflow set     | V                     |  |  |  |  |  |  |  |

| HI.                                                               | higher than    | !(C + Z)  | PL | plus             | !N                    |  |  |  |  |  |  |  |

| LS"                                                               | lower or same  | C + Z     | M  | minus            | N                     |  |  |  |  |  |  |  |

| HS", CC°                                                          | higher or same | !C        | GE | greater or equal | !(N ⊕ V)              |  |  |  |  |  |  |  |

| LOu, CSa                                                          | lower than     | C         | LT | less than        | (N ⊕ V)               |  |  |  |  |  |  |  |

| NE                                                                | not equal      | <u>!Z</u> | GT | greater than     | $![(N \oplus V) + Z]$ |  |  |  |  |  |  |  |

| EQ                                                                | equal          | Z         | LE | less or equal    | $(N \oplus V) + Z$    |  |  |  |  |  |  |  |

Revised by Peter Csaszar, Lawrence Tech University - 2004-2006

- An Address register (16/32-bit, n=0-7) On Data register (8/16/32-bit, n=0-7)

- Rn any data or address register s Source, d Destination

- Either source or destination

- #n Immediate data, i Displacement BCD Binary Coded Decimal

- Effective address

- Long only; all others are byte only Assembler calculates offset

- SSP Supervisor Stack Pointer (32-bit) USP User Stack Pointer (32-bit)

- SP Active Stack Pointer (same as A7)

- PC Program Counter (24-bit)

- SR Status Register (16-bit)

- CCR Condition Code Register (lower 8-bits of SR)

- N negative, Z zero, V overflow, C carry, X extend

- \* set according to operation's result, ≡ set directly - not affected, O cleared, 1 set, U undefined

Branch sizes: **B** or **.S** -128 to +127 bytes, .**W** or **.L** -32768 to +32757 bytes Assembler automatically uses A, I, Q or **M** form if possible. Use #n.L to prevent Quick optimization

Distributed under the GNU general public use license.